分类: 嵌入式

2010-03-08 14:56:30

ADDR_SJA1000_ADDR = ioremap(0x20000000,0xf);

ADDR_SJA1000_DATA = ADDR_SJA1000_ADDR + (0x1<<2);

void write_can_reg(char value, int reg)

{

outb(reg, ADDR_SJA1000_ADDR);

udelay(5);

outb(value, ADDR_SJA1000_DATA);

}

至于为什么是addr然后data,这是芯片制造者的事,可以参考数据手册。同时这与dma9000网卡驱动类似。----关键是sja1000的地址/数据信号线复用,而2410地址数据线分离,所以要模拟ale控制。(说到底还是时序,模拟地址)

由于ARM总线非复用,而SJA1000总线复用,所以必须通过逻辑产生地址锁存信号ALE,假设该信号由芯片GAL22V10产生。SJA1000的片选、读写信号均采用ARM总线信号,ALE信号由读写信号和地址信号通过GAL产生。在写SJA1000寄存器时,首先往总线的一个地址写数据,作为地址,读写信号无效,ALE变化产生锁存信号;然后写另外一个地址,读写信号有效,作为数据。上述逻辑完全通过GAL产生。此外,CAN总线需要在两线问加一个120欧电阻。

2410+sja1000简单接法

1、sja1000的数据总线和arm的数据总线直接连接,arm的地址线a0与sja1000的ale连接,sja1000的片选信号通过由arm的bank片选信号与地址a0取或信号。

2、写数据时,先通过arm的数据总线往sja1000送地址信号,此时a0置1;然后将a0置0,再由arm的数据总线往sja1000送数据信号。

3、读数据时,同样先通过arm的数据总线往sja1000送地址信号,然后取数。

CAN 总线通信控制芯片SJA1000 的读写

CAN 总

线通信控制芯片SJA1000 没有提供单独的地址线,而使用可以与Intel 和Motorola系列微控制器兼容的分时复用地址/

数据线。在一个读写周期内,微控制器首先输出操作地址并使地址锁存信号ALE 有效,SJA1000 在ALE

信号的下降沿将操作地址锁在片内;之后微处理器发出读写信号进行数据传输。但S3C44B0x 的数据线和地址线是分离的,对SJA1000

的读写操作需要模拟微控制器,先在数据线上写一个操作地址,并模拟产生一个ALE

信号锁存这个地址,之后进行正常的读写操作。系统使用地址线ADDR0 区分地址传输和数据传输:写奇地址时,不选通SJA1000

芯片,但给出一个有效的模拟ALE 信号;读写偶地址时,选通SJA1000 读写数据。另外,系统同时有两路CAN 总线接口,读写操作根据地址线ADDR1 区分两个SJA1000 芯片,两个片选信号和ALE 信号都要通过GAL 芯片产生,各信号如图所示。

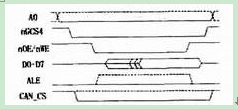

图 SJA1000 控制信号的产生

图中虚线是向SJA1000 传输和锁存地址的过程,实线是读写操作的过程。用ABEL 语言书写的各信号产生逻辑式为:

CAN-CS = nGCS4 # ADDR0 ; (#---或)

ALE = ! nWE &ADDR0 & ! nGCS4 ;

对SJA1000 的操作地址如下:地址锁存向0x08000001端口写地址;数据读写通过地址0x08000000。(地址如何计算,2410 32位地址总线,用到30位,由addr[29::27]选通ngcsx)

Sja1000重要寄存器:

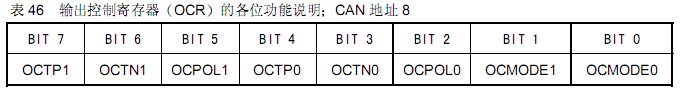

输出控制寄存器(OCR)--复位模式下可读写

b1b0—10---正常模式

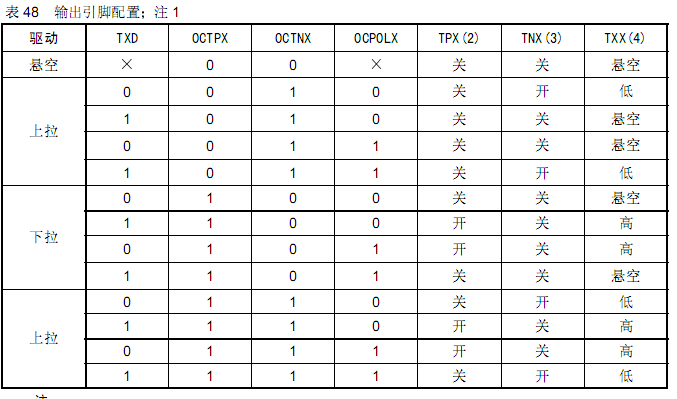

对 于输出控制寄存器的位和输出引脚 TX0 和 TX1 的关系,我的理解是OCTPx,OCTNx编程驱动器特性:00—悬空,01—上拉,10—下拉,11--推挽;OCPOLx编程输出端极性,TX的输出 由TXD(输入)和OCTPx,OCTNx,OCPOLx决定,网上有人根据表格画出卡诺图求出了输入输出的关系。OCPOLx为0,当TPX与TNX并 非全关状态时候,OCPOLx为0,输出电平与TXD一致,为1翻转。TPX与TNX全关状态输出管脚悬空。

所以电路中要用到TX0(使TX0与TXD输入相同,为什么?)并使TX1设置悬空,OCTP0,OCTN0,OCPOL0要设为110,OCTP1,OCTN1,OCPOL1就设为000,则输出控制寄存器设置应该为0x1a

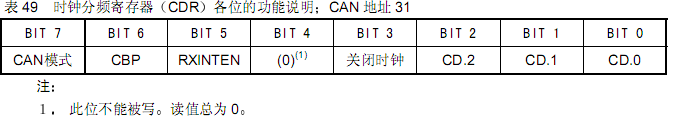

时钟分频寄存器(CDR)

一 般用不到sja1000的clkout管脚,所有bit3置1,CD.2—CD.0用来设置clkout管脚上的频率,这里也用不上。Bit5是允许接受 中断输出,当一条已接收的信息成功的通过验收滤波器一位时间长度的接收中断脉冲就会在 TX1 引脚输出(帧的最后一位期间),发送输出阶段应该工作在正常输出模式。

BIT6,CBP置位,激活 SJA1000 的比较器旁路功能,如果这个功能被使能,施密特触发器有效,内部的传播延迟 tD2 比接收比较器延迟的 tD1 要小得多 这在最大总线长度(can协议规约)上有积极的影响

Bit7:0—basic模式,1—pelican

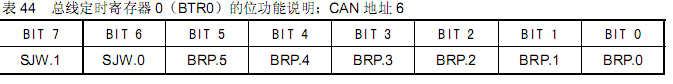

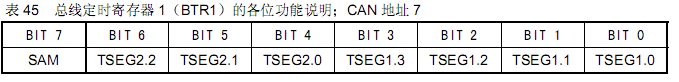

总线定时寄存器(BTR):

该寄存器很重要,要设定can总线的位定时参数,这个要从总线原理入手,不是一下就能理解的,但给定了需要的参数后要会怎么编程设定。

BRP:波特率预分频值

CAN 系统时钟 tSCL 的周期是可编程的 而且决定了相应的位时序 CAN 系统时钟.由如下公式计算

tSCL=2 tCLK (32 BRP.5+16 BRP.4+8 BRP.3+4 BRP.2+2 BRP.1+BRP.0+1)

这里 tCLK =XTAL 的频率周期=1/fXTAL

![]()

(Sja1000内部频率基准源F_BASE = Fclk/2,即外部晶振频率Fclk的2分频。注意任何应用中,当利用外部晶振作为基准源的时候,都是先经过2分频整形的。)

一个位时间(位速率就是其倒数):

![]()

如下图:

tSYNCSEG=1*tSCL (固定长度)

tTSEG1=tSCL*(8 TSEG1.3+4 TSEG1.2+2 TSEG1.1+TSEG1.0+1)

tTSEG2=tSCL*(4 TSEG2.2+2 TSEG2.1+TSEG2.1+1)

同步跳转宽度(sjw)定义了每一位周期可以被重新同步缩短或延长的时钟周期的最大数目:

tSJW=tSCL (2 SJW.1+SJW.0+1)

【总结】:就以上关系式来看,首先可以设定一个位周期由几个段组成,这样

1/((TEG1+TEG2+1)*tSCL)=1/tBit=波特率(注意TEG的值是十六进制换算后加1,见上表)

其中tSCL=2tCLK*BRP(tCLK为sja1000外部晶振)(同上,BRP也是换算后加1),由此可由指定波特率及给定can总线频率去定BRP及TEG的设定。

问题在于:不知道TEG(即相位缓冲段)的分配不同有何影响,和同步跳转宽度设定的实际意义。

查 找资料得出,以上的计算是理论值。“在实际的网络通信中由于存在传输的延时、不同节点的晶体的误差等因素,使得网络CAN的波特率的计算变得复杂起来。 CAN在技术上便引入了重同步的概念,以 更好的解决这些问题。这样重同步带来的结果就是要么时间段1(Tseg1)增加TSJW(同步跳转宽度SJW+1),要么时间段减少TSJW,因此CAN 的波特率实际上有一个范围:1/(Tbit+Tsjw) ≤CANbps≤1/(Tbit-Tsjw)” “而 TSEG1与TSEG2又是怎么划分的呢?TSEG1与TSEG2的长度决定了CAN数据的采样点,这种方式允许宽范围的数据传输延迟和晶体的误差。其中 TSEG1用来调整数据传输延迟时间造成的误差,而TSEG2则用来调整不同点节点晶体频率的误差。但是他们由于过于灵活,而使初次接触CAN的人有点无 所适从。TSEG1与TSEG2的是分大体遵循以下规则: Tseg2≥Tscl2,Tseg2≥2TSJW,Tseg1≥Tseg2”————http://blog.chinaunix.net/u3/93821/showart_2050196.html

【举例说明】:外部晶振24M 要求波特率133k,can总线频率1.33M(时间冲量长度751.87ns),同步跳转宽度3,时间段1长度为6,时间段2长度为3,每位采样一次。

显然这是一个位周期十个段的,可设置好TEG1 TEG2 及TJW 和SAW,接下来就是计算BRP。根据tBit/10=2tCLK*BRP得BRP=fClk/(2*10fBit)=24/(2*10*1.33)

验收代码及验收屏蔽寄存器(ACR、AMR)

满足[ ID.10-ID.3=AC.7-AC.0 ] |[AM.7-AM.0]= 11111111方程的即可接收。

BasicCAN 模式里的验收滤波:

在这个模式 SJA1000 可以即插即用地取代 PCA

例如:

验收代码寄存器ACR:01110010

验收屏蔽寄存器AMR:00111000

11位ID信息:01XXX010XXX

在验收屏蔽寄存器里1 的位置上,ID在这位的任何值都被允许,对于三个最低位同样,因此 64 个不同的 ID 在这个例子里可被接收,其他位置的位必须等于验收代码寄存器相应位的值。

命令寄存器 CMR (PeliCAN模式下没有这个寄存器)

一般情况:

执行读取命令---0x04,即释放接收缓冲器。读接收缓冲器之后 CPU 可以通过设置释放接收缓冲器位为 1 来释放 RXFIFO 的内存空间,这样就会导致接收缓冲器内的另一条信息立即有效,如果没有其它有用的信息,就复位接收中断

执行写入命令—0x01,即发送请求位置1.可通过CMR.1中止发送位置1取消发送;

控制寄存器(CR)(PeliCAN模式下没有这个寄存器)

0x01—进入复位模式。进入工作模式要将CR.0置0, 复位请求位接收到一个下降沿后,SJA1000回到工作模式。

该寄存器还设置使能中断等位,详见datasheet。

ps: CAN协议规定的最小时间——128 个总线空闲信号(总线空闲信号是什么?)

中断寄存器(IR)

中 断寄存器中我们主要关注接收中断RI---接收FIFO不空且中断寄存器的RIE位被置位时此位被置1。注意,CPU读中断寄存器的时候,除了接收中断外 的所有位都被复位。释放接收缓冲器的命令(CMR---0X04)可以临时清除 RI 如果执行释放命令后 FIFO中还有可用信息 RI 被重新置位 否则 RI 保持清 0 状态 。

注意:在PeliCAN模式里中断的使能禁能是使用内部寄存器地址4的IER,而BasicCAN模式下则用的是控制寄存器CR(PeliCAN模式里内部寄存器地址0用作MOD寄存器)

在驱动的编写过程中,发送数据可以不用中断,读数据时候可以利用等待队列以及接收中断。