分类: 嵌入式

2011-05-05 13:21:11

西安电子科技大学 童庆平,刘笃仁

引言

S3C2410是三星公司生产的基于ARM920T内核的RISC微处理器,主频率可达203MHz,适用于信息家电、Smart Phone、Tablet、手持设备、移动终端等领域。其中,集成的LCD控制器具有通用性,可与大多数的LCD显示模块接口。

PD064VT5是一种用非晶硅TFT作为开关器件的有源矩阵液晶显示器,该模块包括TFT-LCD显示屏、驱动电路和背光源,其接口为TTL电平。分辨率为640 x480像素,可通过18bit数据信号显示262 144种色彩。

1 S3C2410的LCD控制器

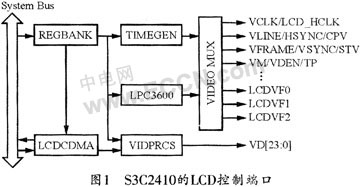

S3C2410中的LCD控制器可用于传输视频数据并产生必要的控制信号(像VFRAME、VLINE、VCLK、VM等)。S3C2410的输出视频数据端口VD [23:0]的示意图如图1所示。

通常使用的LCD控制管脚的定义如下:

VCLK:像素时钟信号;

VD [23:0]:LCD像素输出端口;

VM/VDEN/TP:LCD驱动器的AC偏置信号(STN)/数据使能信号(TFT)/SEC TFT源驱动器数据加载脉冲信号复用端口。

1.1 S3C2410中的LCD控制寄存器

S3C2410的LCD控制寄存器主要有LCDCON1寄存器、LCDCON2寄存器、LCDCON3寄存器、LCDCON4寄存器和LCDCON5寄存器。

1.2 控制流程

由图1可见,S3C2410中的LCD控制器由REGBANK、LCDCDMA、VIDPRCS、TIMEGEN和LPC3600组成。其中 REGBANK有17个可编程寄存器组和256x16的调色板存储器,可用来设定LCD控制器;LCDCDMA是一个专用DMA,可自动从帧存储器传输视 频数据到LCD控制器,通过这个特殊的DMA,视频数据可不经过CPU处理就在屏幕上显示;VIDPRCS可接收从LCDCDMA来的视频数据并将其修改 到合适数据格式,然后经VD[23:0]送到LCD驱动器,如4/8单扫描或4双扫描显示模式;TIMEGEN则由可编程逻辑组成,可支持不同LCD驱动 器接口时序和不同的速率,TIMEGEN用于产生VFRAME、VLINE、VCLK、VM等信号。

FIFO存储器通常位于LCDCDMA。当FIFO为空或部分为空时,LCDCDMA要求从基于突发传输模式的帧存储器中取出数据并存入要显示的图像数 据,而这帧存储器是LCD控制器在RAM中开辟的一片缓冲区。当这个传输请求被存储控制器中的总线仲裁器接收后,系统存储器就给内部FIFO成功传输4个 字。FIFO的总大小是28个字。其中低位FIFOL是12个字,高位FIFOH是16个字。S3C2410有两个FIFO,可支持双扫描显示模式。但在 单扫描模式下只使用一个FIFO (FIFOH)。

1.3 TFT控制器操作

S3C2410可支持STN-LCD和TFT-LCD,这里只介绍其对TFT-LCD的控制。TIMEGEN可产生LCD驱动器的控制信号(如 VSYNC、HSYNC、VCLK、VDEN和LEND等)。这些控制信号与REGBANK寄存器组中的LCDCON1/2/3/4/5寄存器的配置关系 相当密切。基于LCD控制寄存器中的这些可编程配置,TIMEGEN便可产生可编程控制信号来支持不同类型的LCD驱动器。而VSYNC和 HSYNC脉冲的产生则依赖于LCD-CON2/3寄存器的HOZVAL域和LINEVAL域的配置。HOZVAL和L NEVAL的值由LCD屏的尺寸决定:

HOZVAL=水平显示尺寸-1 (1)

LINEVAL=垂直显示尺寸-1 (2)

VCLK信号的频率取决于LCDCON1寄存器中的CLKVAL域。VCLK和CLKVAL的关系如下(其中CLKVAL的最小值是0):

VCLK(Hz)=HCLK/[(CLKVAL+1)x2] (3)

一般情况下,帧频率就是VSYNC信号的频率,它与LCDCON1和LCDCON2/3/4寄存器的VSYNC、VB2PD、VFPD、LINEVAL、 HSYNC、HBPD、HFPD、HOZVAL和CLKVAL都有关系。大多数LCD驱动器都需要与显示器相匹配的帧频率,帧频率计算公式如下:

Frame Rate=1{[(VSPW+1)+(VBPD+1)+(LINEVAL+1)+(VFPD+1)]×[(HSPW+1)+(HBPD+1)+(HFPD+1)+(HOZVAL+1)]×[2×(CLKVAL+1)/(HCLK)]} (4)

参照PD064VT5的参数和公式(1)、(2)可得出:HOZVAL=639;LINEVAL=479。其余主要寄存器的值在下面给出。

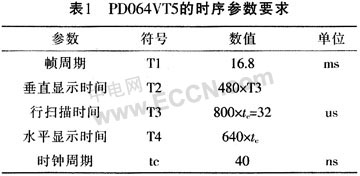

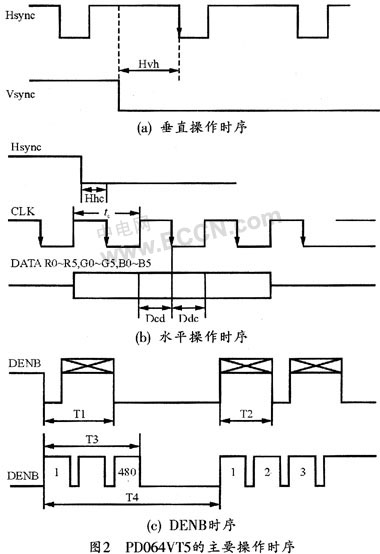

2 PD064VT5的逻辑时序

PD064VT5的时序参数如表1所列,图2所示是PD064VT5的主要操作时序。根据该时序要求,设计时可设定VM/VDEN信号作为LCD的 ENAB信号,VCLK信号作为LCD的NCLK信号。要想得到合适的VM和VCLK波形,就要正确设定寄存器的值,并根据寄存器的值与VM和VCLK波 形的关系设定如下关键寄存器的值:

HSPW=10;HBPD=100;HFPD=47;

VSPW=1;VBPD=37;VFPD=4

由于S3C2410的HCLK工作频率大多在100MHz左右,因此,根据公式(3)可设CLKVAL=1。

3 嵌入式Linux下驱动程序的开发

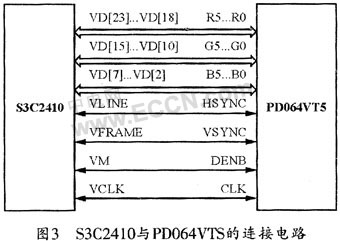

图3所示是S3C2410与PD064VTS的硬件连接电路。

开发该嵌入式系统驱动程序时,FrameBuffer可作为出现在Linux2.2.xx内核当中的一种驱动程序接口。对应的源文件在 linux/driver s/video/目录下,总的抽象设备文件为fbcon.c。这种接口将显示设备抽象为帧缓冲区,用户可以将它看成是显示内存的一个映像。但在使用帧缓冲 时,Linux是将显卡置于图形模式下的。

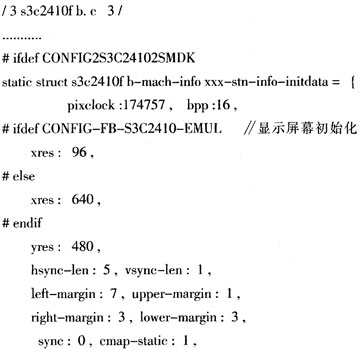

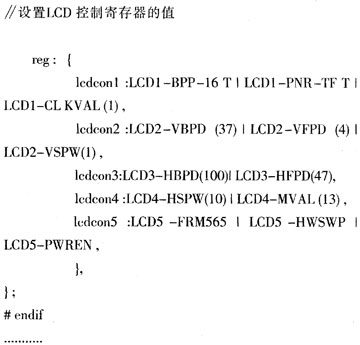

根据以上对LCD各主要寄存器设置的分析所得出的结果,笔者开发了基于FrameBuffer机制的S3C2410fb驱动程序。下面是调试成功的部分代码,作用是初始化显示屏幕和设置LCD控制寄存器的值。

4 结束语

本设计经过硬件方面的调试修改,在S3C2410开发板的VCLK脚和VM脚成功得到了PD064VT5所需的时钟信号和复合控制信号;同时通过在软件方 面修改S3C2410的驱动程序,并经编译整个系统后再重新写到Flash中,可以在重启后正确显示原系统的静态启动画面,而且画面清晰稳定,达到了预期 的效果。该装置可用于工业控制和车载通信等领域的显示输出设备,如再加上适当的触摸屏,还可组成方便可靠的输入输出设备。

|

|